Verilog 从0到60——数电基础

前言-此页面还在更新

第一次尝试写一个长系列。芯片前端开发是一个非常复杂繁琐的过程,受限于家里没有公司的一整套环境,且没有验证和支持人员的配合,因此虽然工作是ASIC芯片,但在家只能用Quartus进行代码编写和仿真,以及玩一玩FPGA。本文和实际尚有出入,主要是为了帮助自己深化基础功力,同时分享心得。

转载请注明来源并获得我的同意。email: xinb@outlook.it

二进制数

二进制数和16进制数的转换

一般来说,4位二进制数恰好能表示一位16进制数,因此16进制是硬件描述语言中第二常用的进制。16 进制的 f 即为 二进制的1111。转换方法属于基础知识,不在此赘述。

二进制数的编码

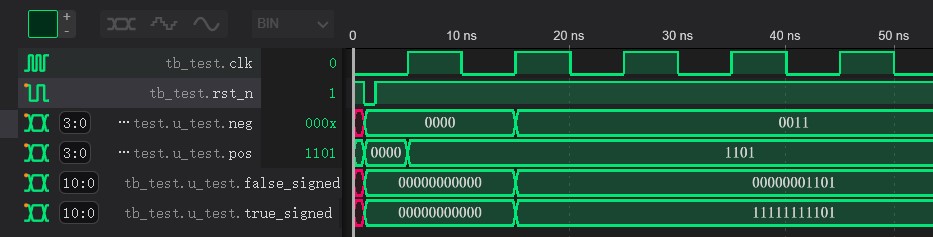

这里主要需要掌握二进制数的原码、补码。因为在verilog中有符号数是用补码保存的,同时补码也能非常方便的求负数,如下:neg是pos的负数,true_signed和false_signed展示了有、无符号数的区别。其实,verilog中有符号数和无符号数的区别在于扩位方式不同。

reg signed [3:0] pos,neg;

reg [10:0] false_signed;

reg [10:0] true_signed;

reg signed [3:0] num_true_signed;

reg [3:0] num_false_signed;

always @(posedge clk or negedge rst_n) begin

if (!rst_n)begin

pos <= 4'b0;

neg <= 4'b0;

false_signed <= 'b0;

true_signed <= 'b0;

num_true_signed <= 'b0;

num_false_signed <= 'b0;

end

else begin

pos <= 1101; //对其直接赋值二进制,等效pos = -2

neg <= ~(pos) + 1;

num_true_signed <= 4'b1101;

num_false_signed <= 4'b1101;

true_signed <= num_true_signed;

逻辑操作

包括逻辑操作、按位操作、归约操作

逻辑操作

A = 3;

B = 0;

C = 2'b1x ;

A && B // 为假

A || B // 为真

! A // 为假

! B // 为真

A && C // 为X,不确定

A || C // 为真,因为A为真

(A==2) && (! B) //为真,此时第一个操作数为表达式

按位操作

A = 4'b0101 ;

B = 4'b1001 ;

C = 4'bx010 ;

~A //4'b1010

A & B //4'b0001

A | B //4'b1101

A^B //4'b1100 异或

A ~^ B //4'b0011 同或

B | C //4'b1011

B&C //4'bx000

规约操作

A = 4'b1010 ;

&A ; //结果为 1 & 0 & 1 & 0 = 1'b0,可用来判断变量A是否全1

~|A ; //结果为 ~(1 | 0 | 1 | 0) = 1'b0, 可用来判断变量A是否为全0

^A ; //结果为 1 ^ 0 ^ 1 ^ 0 = 1'b0

版权声明:

作者:xinbao

链接:https://ixinb.com/verilog/verilog-%e4%bb%8e0%e5%88%b060-%e6%95%b0%e7%94%b5%e5%9f%ba%e7%a1%80/

文章版权归作者所有,未经允许请勿转载。

THE END